東芝のフラッシュメモリ

2017年7月25日

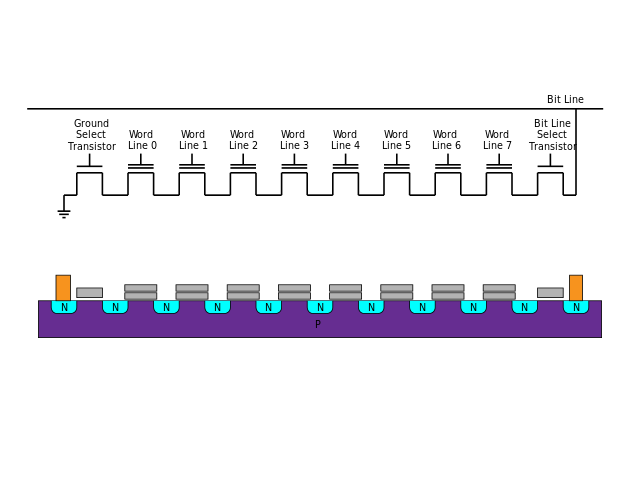

(画像、ベースとなるNAND型フラッシュメモリ構造)

フラッシュメモリは舛岡富士雄氏によるNOR型とNAND型のフラッシュメモリを発明したのが始まりです。

その後技術革新が進んでフラッシュメモリの微細化が進みます。

微細化が進んだ後に近年ではフラッシュメモリは三次元積層構造へと技術の進化が進んでいます。

そして「多値化」も進んでいます。

三次元フラッシュメモリ

2007年に東芝メモリは三次元積層構造のフラッシュメモリの世界初の公表をしています。

それからフラッシュメモリの開発は世界的にどんどん進んできています。

現在ではサムスン電子がフラッシュメモリシェア世界首位になっています。

しかし現在でも日本国内では東芝メモリが四日市の工場施設で新たな三次元フラッシュメモリの試作・開発を進め続けています。

それは「BiCS FLASH」というメモリです。

「この「BiCS FLASH」はシリコン平面から垂直方向にフラッシュメモリ素子を積み上げた構造をしています。シリコン平面上にフラッシュメモリを並べたNAND構造とは違う構造です。」

(「」、TOSHIBA、半導体&ストレージ製品 ホーム→製品→メモリ→BiCS FLASH、BiCS FLASHの特長より引用)

2017年8月7日~10日にアメリカのサンタクララで「Flash Memory Summit2017」が開催されます。

東芝メモリはこのイベントでの参考展示に向けて「BiCS FLASH」の新たな構造の三次元積層構造のフラッシュメモリの試作・開発を続けています。

「フラッシュメモリは1つのセルの浮遊ゲートに電子を蓄積する電荷量によって区別されます。

1つのセルの浮遊ゲートに1bitの情報を記録する方式をSingle Level Cell略して「SLC」、電荷量の区別により2bitのものをMulti Level Cell「MLC」、3bitのものをTriple Level Cell「TLC」などといいます。」

(「」、NAND型フラッシュメモリ、SLCとMLC Wikipediaより引用)

東芝メモリが新しく試作しているのは世界初の1つのセルの浮遊ゲートに4bit(「QLC」といいます)の情報を記録する技術方式の三次元積層構造フラッシュメモリ「BiCS FLASH」です。

従来の「TLC」に比べてセルあたりの浮遊ゲート記録可能bit数が1つ増えることでより大容量のメモリが製造可能になります。

この「QLC」「BiCS FLASH」がFlash Memory Summit2017に参考展示される模様です。

東芝メモリの試作・開発技術の近況

東芝は試作品段階で「TLC」で96層の256Gbit(32GB相当)のメモリ生産を達成しています。

また、「QLC」では64層積層プロセス768Gbit(96GB相当)を実現しています。

東芝メモリは「QLC」の64層積層プロセス768Gbit(96GB相当)のチップを1パッケージに16段積層する業界最大容量の1.5TB相当の製品を2017年後期にサンプル出荷、2018年に量産化する予定です。

四日市の工場ではさらなる積層プロセスの三次元積層構造フラッシュメモリの製品化も計画しています。

これらはさまざまなかたちで商品化が期待できるSSDです。

ノーベル化学賞を受賞した田中耕一さんの「研究費がたくさんある時もいい研究ができるが、逆に切羽詰まってこれしかないという時にいいものが生まれる」という言葉を信じたい、筆者はそんな気持ちです。